# 1.2 五大機能とハードウェア

## 1.2.1 CPU

## ■ CPU の機能

CPU は、演算処理や制御処理を行う、コンピューターの中枢となる部品です。「中央演算処理装置」とも呼ばれます。

パソコンで使われる CPU のメーカーとして、Intel や AMD などがあります。両社とも一般的なデスクトップパソコン用のみならず、サーバー向けやノートパソコン向け CPU などを提供しています。主な CPU のブランド名には、次のようなものがあります。

表 1.2-1 CPU のブランド名

| メーカー名 | CPU のブランド名                            |

|-------|---------------------------------------|

| Intel | Core™ i シリーズ, Pentium®, Celeron®      |

| AMD   | Ryzen™ Threadripper™, Ryzen™, Athlon™ |

## ■ CPU の構造

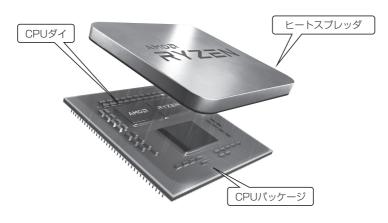

CPUは、下図のように様々な機能をもつ部品により構成されています。

図 1.2-1 CPU の構造

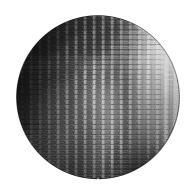

CPUの中心となる部品は、「CPUダイ」と呼ばれる半導体チップです。CPUダイは、シリコンウェハーと呼ばれる薄い円盤に回路や素子を焼き付けて製造されます。1枚のシリコンウェハ

ーには数百個の同じ半導体チップが焼き付けられており、それを切手のように1枚ずつ切り出すことで、一つのチップになります。一つのチップは数 mm 角から大きくても数十 mm 角であり、このサイズのことをダイサイズと呼びます。

写真 1.2-1 シリコンウェハーと CPU ダイ

前述の通り CPU ダイは非常に小さな部品のため、接点を設けたり破損を防ぐために専用の基板上に実装されています。基板上に実装された状態の CPU を CPU パッケージと呼びます。

CPU パッケージの底面にはマザーボード上のソケットと接続される接点が備えられており、 用途に応じて幾つかのパッケージがあります。

| 名称                    | 解説<br>解説                             |

|-----------------------|--------------------------------------|

| PGA (Pin Grid Array)  | 剣山のように多数のピンを設け、ソケットに差し込むように装着する。     |

| LGA (Land Grid Array) | 小さな電極を多数設け、ソケットに押しつけるように装着する。        |

| BGA (Ball Grid Array) | 半球状になったハンダ製の端子が設けられ、加熱しハンダを溶かして装着する。 |

表 1.2-2 CPU パッケージの例

放熱や保護のため CPU ダイは「ヒートスプレッダ」と呼ばれる部品で覆われています。ヒートスプレッダと CPU ダイの間は、TIM (Thermal Interface Material) と呼ばれるハンダやシリコングリスを介して接続されており、効率的に放熱を行うことができるようになっています。

### コラム: CPU の価格はどうやってきまる?

CPU は、同じシリーズの中でも、動作クロックやコア数、グラフィック機能の有無など、様々な性能を持つモデルがラインナップされています。しかしながら、同一シリーズの CPU であれば、それらの内部回路はほとんど同じものです。

前述で、1 枚のシリコンウェハーから多数の CPU ダイが切り出されることを説明しました。シリコンウェハーから切り出された CPU ダイを検査する工程の中で、それぞれの CPU ダイが正しく動作しているか、どのぐらいの性能で動作するかを検査します。

それらの中には、すべてが正常に動作するもの、まったく動かないものの他に、一部の機能が正しく動かないものがあります。例えばキャッシュの一部を認識しない CPU ダイや、CPU コアの半分が正しく動かない CPU ダイなどがあります。それらは異常が発生している回路を切断した上で下位のモデルとなります。

また低い電圧でも高いクロックで動作する CPU ダイは低消費電力モデル、より高いクロックで動作する CPU ダイは上位モデル、といったように性能別にチップを振り分けます。この作業を「選別」と呼んでいます。

より高い動作クロックで動作する CPU ダイやまったく不具合箇所がない CPU ダイは、製造された CPU ダイの中でも限られた数しか製造できません。希少価値が高いため、価格はもちろん高価になります。

高性能・高機能の CPU を実現するためには、大規模な回路を実装する必要があり、回路の規模に応じて必要な CPU ダイの面積は大きくなります。1 枚のシリコンウェハーから切り出すことができる CPU ダイが少なければ、大量生産することが困難になり、自ずと価格は高価になります。また、CPU ダイの面積が増えれば増えるほど、異常がない CPU ダイの数も少なくなります。

より大規模な回路を小さな面積に収めるために行われる手法として「プロセス・ルールの微細化」があります。プロセス・ルールとは CPU 内の回路で用いられる配線の幅を示し、小さければ小さいほど、同じ面積に大規模な回路を実装することができます。例えばプロセス・ルールが半分になれば、同じ面積に 4 倍の回路を配置できます。また回路長が短くなることにより動作クロックも向上し、より少ない電力で動作させることが可能になります。但し、製造にはより高度な技術が必要になります。

2000 年に発売された Pentium 4 プロセッサでは 180nm プロセスが利用されていましたが、2017 年に発売された第 8 世代 Core プロセッサでは 14nm プロセスが採用されています。実装されるトランジスタ数を比較すると前者が 4200 万に対し、後者は 17 億個となります。

## CPU 内部の仕組み

CPU は、プログラムや OS が実行する命令を直接解釈できるわけではなく、2 進数の機械語を用いた四則演算や論理演算、データのコピーなど、単純な処理に分解して演算を行っています。

CPU が解釈できる命令の集合体を「命令セット」と呼び、命令セットの構成や各命令の動作 方法を定めたものを「命令セットアーキテクチャ」と呼びます。

現在我々が使っているほとんどのコンピューターは「x86」命令セットアーキテクチャ、及び その派生である「x86-64 (AMD64, Intel64)」が用いられています。

また、その命令セットを実行できる回路の設計、実装方法を「マイクロアーキテクチャ」と呼びます。

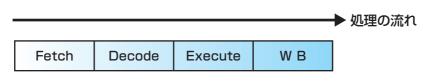

CPU 内部で実行される処理の流れを下図に示します。

図 1.2-2 CPU 演算の流れ

- 1. Fetch (フェッチ)

- メモリ上に格納された命令を制御装置に読み込みます。

- 2. Decode (デコード)

- 読み込まれた命令を元に、演算手法や動作方法を解釈します。

- 3. Execute (エグゼキュート)

- 分解された命令を元に、演算装置を用いて四則演算や論理演算を行います。

- 4. WriteBack (ライトバック) レジスタ、キャッシュメモリ、インターフェイスを介して、演算結果を書き出します。

上記のような演算を行うため、CPU内部には、次の様な回路が実装されています。

- ·制御装置

- 命令の解釈や演算装置などへの動作を指示し、プロセッサ全体の処理を制御する部分です。

- ·演算装置 (ALU, FPU)

制御装置とともに CPU の中心となる機能で、整数演算や論理演算などの基本的な演算を行う算術論理演算装置 (ALU) と、浮動小数点数の計算に特化した浮動小数点演算装置 (FPU) にわけられます。

#### NOTE

ALU: Arithmetic and Logic Unit FPU: Floating Point Unit

#### ・レジスタ

演算や命令などの処理を行うためのデータを保持するための記憶領域で、演算装置や制御装置に直接接続されており、メインメモリと比較してより高速な処理が可能です。

演算に利用するデータは、メインメモリやキャッシュメモリから読み込まれ、レジスタに格納 されます。また演算結果はレジスタからメインメモリやキャッシュメモリに書き出されます。

・キャッシュメモリ

レジスタとメインメモリの間で、速度や容量の性能差を埋めるために用いられる、高速で小容量のメモリを指します。昨今の CPU では、L1, L2, L3 など、レベルに合わせた複数の速度・容量を持つキャッシュメモリが搭載されています。

・インターフェイス

メインメモリや外部バスなど、コンピューターを構成するその他の要素と接続される部分の ことで、信号の入出力はすべてこのインターフェイスを通して行われます。

#### CPU の性能

CPU の性能を示す指標としては、「クロック周波数」と「IPC」が用いられ、下記のような計算式で表されます。

Performance (性能) = Frequency (周波数) × IPC

CPU 内では、複雑な処理を「命令」と呼ばれる単純な処理に分割し、クロック周波数のタイミングに合わせて実行しています。 たとえば 3GHz の CPU では、1 秒間に  $3 \times 10$  の 9 乗 = 30 億回のクロックに合わせて命令が実行されます。

また、「IPC」とは、1クロックで実行できる命令の数を表します。IPC は CPU 内部の設計やアーキテクチャにより異なります。

同じクロック周波数の CPU であっても、IPC が異なれば CPU が持つ演算性能は異なります。 逆を言えば、同じ IPC を持つ CPU であれば、クロック周波数が高ければ高いほど、演算性能 は向上します。

#### NOTE

IPC: Instruction Per Clock

## ■ CPU の高速化技術

CPU のクロック周波数と IPC は、コンピューターの進化とともに向上してきました。しかしながら、昨今ではクロック周波数と IPC の向上だけでは、市場から要求される演算性能に追いつかなくなってきました。

例えば、クロック周波数を向上させれば、CPU からの発熱が大きくなります。また、IPC を向上させるためには、より複雑な演算装置を CPU 内部に実装しなくてはならず、コスト上昇を招きます。そのため、それ以外の方法で CPU 自体の処理能力を向上させる手法がとられています。・拡張命令

CPU内部では様々な処理を「命令」という形で解釈し、それらを分解して演算しています。 それら命令の集合体を「命令セット」と呼び、一般的に利用されているパソコンでは、インテルが開発した「x86」命令セット、及びそれを元に 64bit 化した「x86-64」という命令セットが使われています。

OSやアプリケーションなどのすべてのソフトウェアは命令セットに従って動作をしますが、それらを CPU メーカーが独自に拡張し特定の処理に特化した命令セットを追加することで、より高速で効率的な処理を実現しています。動画や音楽のエンコードなど、マルチメディア処理では大きな恩恵を得られますが、対応した CPU とアプリケーションを必要とします。代表的な拡張命令セットとして、「SSE | 「AVX | が挙げられます。

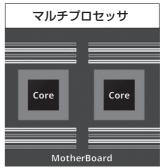

・マルチプロセッサとマルチコアプロセッサ

従来より、サーバーやワークステーションなどの高い能力を必要とするコンピューターでは、システムの処理能力を向上させるため、マザーボード上に複数個の CPU を実装する「マルチプロセッサ」という技術が用いられてきました。

しかしながら、複数の CPU を一つのシステムに実装するためには、マザーボードや筐体のサイズが大きくなったり、大容量の電源ユニットを必要とするなど、大きなコストがかかってしまうことが問題でした。

そのため昨今のプロセッサには、「マルチコアプロセッサ」「同時マルチスレッディング技術」といった、一つの CPU 内で物理的・論理的にコア数を増やす技術が採用されています。

「マルチコアプロセッサ」は、一つの CPU パッケージ内に複数のプロセッサコアを内蔵したものです。コアが2つであればデュアルコア、4つであればクアッドコア、8つであればオクタコアと呼ばれます。それに対して、コアを一つしか持たない従来からのプロセッサを「シングルコアプロセッサ」と呼ぶこともあります。

プロセッサコアの中でも、共有することが容易な2次・3次キャッシュやインターフェイス部分は共有されているため、マルチ CPU と比較して性能的なメリットもあります。

図 1.2-3:マルチコアプロセッサ

## ・同時マルチスレッディング技術

同時マルチスレッディング技術(SMT)とは、CPUコア内部の回路の一部を二重化し、 演算回路などの利用効率をあげるための技術です。物理的なコア数はかわりませんが、OS 側から見た場合は複数のコアが実装されているように認識されます。

元々は処理能力を向上するための技術ではなく、CPU 内部の回路をより効率的に利用するための技術でした。

同時マルチスレッディング技術を採用した CPU の代表として、Intel 社のハイパースレッディング(Hyper Threading)があります。

この技術を採用した CPU の多くは、物理コア数と論理コア数(スレッド数)と表記されており、搭載されていない CPU と見分けることが可能です。マルチコア CPU とは違い、例え論理コア数が 2 倍になったとしても、実際の性能は 2 倍にならないことがほとんどです。

以下に、Windows にてコア数を確認できる画面を例示します。この画面では、物理コア数は「コア」、論理コア数は「論理プロセッサ数」と表示されています。

#### NOTE

SMT: Simultaneous Multi Thread